# Secure compilation

with the compiler, not against

First experiments on "Tracing LLVM"

Sébastien MICHELLAND (UGA/LCIS, Valence)

Journées Nationales du GDR Sécurité 2025 — June 24th, 2025

# Your last speaker of the day!

#### Sébastien Michelland

- ➤ 3rd-year Ph.D student at LCIS (Valence)

- Advised by Laure Gonnord and Christophe Deleuze

- Compilers

- Embedded systems

- ► Formal verification (\* rainy days only)

# Dealing with fault injection attacks

Fault injection attacks

### Fault injections are wild...

Fault: abnormal condition leading to incorrect behavior

$2+2 \rightarrow \text{something goes wrong} \rightarrow 42$

#### Fault injections are wild...

Fault: abnormal condition leading to incorrect behavior

$2+2 \rightarrow$  something goes wrong  $\rightarrow 42$

Fault injection: creating a fault on purpose

Electromagnetic fault injection [Sol+21]

Power/clock glitches, lasers, EM pulses...

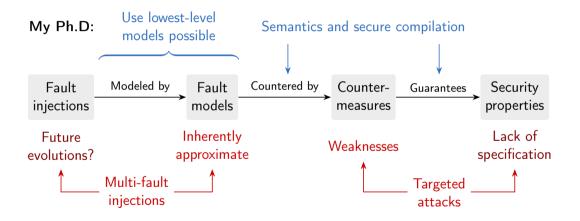

Semantics and secure compilation

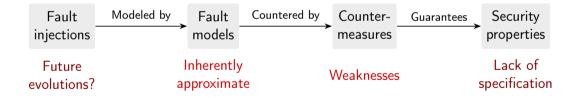

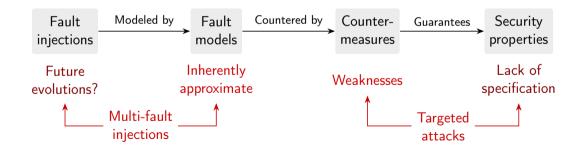

#### Challenges

- Can hardly predict outcomes

- Some consistent behaviors

- Many very rare and very weird behaviors

#### ... so we approximate with fault models.

Fault model: approximate description of common fault behaviors

#### Examples:

Fault injection attacks

- Invert an if()

- Corrupt program values

- Skip instructions

- Cancel pipeline forwarding [Lau20]

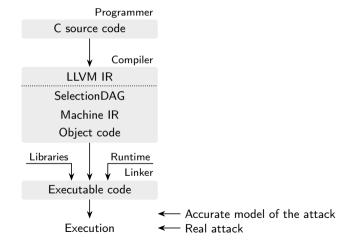

← C source.

■ IR-ish

**⋖** Assembly

■ Micro-arch

Understandable

Accurate

#### ... so we approximate with fault models.

Fault model: approximate description of common fault behaviors

#### Examples:

- ► Invert an if()

- Corrupt program values

- Skip instructions

- ► Cancel pipeline forwarding [Lau20]

- ← C source.

- IR-ish

Semantics and secure compilation

- Assembly

- Micro-arch

#### Understandable

Accurate

#### Inherent tension

Fault models are always a compromise between accuracy and simplicity.

Fault injection attacks

# Use lowest-level models possible

#### Precise attack models are low-level and tricky

Fetch skips by Alshaer et al. [Als+22]

Fault injection attacks

| c.addi a0,a0,1 | lw a0,144(a1) |

|----------------|---------------|

| (lw cont.)     | c.ret         |

▼ Skip 32 bits!

| <del>c.addi a0,a0,1</del> | <del>lw a0,144(a1)</del> |

|---------------------------|--------------------------|

| addi s2, s2, 1            | c.ret                    |

- ► Found on ARM and RISC-V

- Can corrupt instructions

- ► Can affect more than one instruction

#### Typical abstraction compromise!

- ► Brings in pipeline details

- ► More precise than instruction skip

- ► Harder to deal with

# But co-design can deal with them!

Paper: From low-level fault modeling to a proven hardening scheme — CC'24 [MDG24]

Co-designed countermeasure with nice properties!

#### From low-level fault modeling (of a pipeline attack) to a proven hardening scheme

Christophe Deleuze sabastica michallandibleis connoble. christopha delegrasibasenoble inn fr

First attacks present unique safety and security challenges securities. Models of those complex attacks are made workable he representative their effects to a suitable basel of tion Set Architecture (ISA) level just ideal because it discoch impatent micro-soluteched information leafing to weaker neverthy engrantees. Convergely, including microand reason about creating a new challenge in relidating and

We show that a screantic approach to modeling faults malors micro-architectural models workship, and grables designing and implementing a compiler-hardware countermeasure, which protects against a state-of-the-ort pipeline forch attack that progradings multi-fault instruction skins. lead extens embles floor more occurs consterns source

elitch a neger caredy voltage clitch or an electromagnetic al. 2006), sometimes just enough to bypass an application's herd et al. 2021) makes them a taneible threat to modern safety, and negative critical systems. Countering them is that traditional development tools meticulously avoid by building upon a clean abstraction stack from hardware to

In order to conquer the complexity of these attacks, se-

faults' effects to a desired least of obstruction. These soon from hit flas in RTL (Resister Transfer Level) latches [Teller termeasures are then based on these models, so in a sense secure programs resist fault models rather than fealts. The

In practice, most existing works study faults at the ISA struction skins, wrame house, corrupted registers, etc. DAIDer nembler programs. This is a natural choice as assembler is the compiler automation, and the ability to protect only critical common, but better equipped to deal with local and remote

The key issue with ISA-level fault models is that the apther shows that targeted fault attacks can and do defeat less-level effects.

Naturally, using low-level models widens the eletrorism can between the affack and the countermeasure (often an plied during compilation at an IR or back-end level). This the compiler's late stages. These cross-layer concerns (com-

#### But co-design can deal with them!

Fault injection attacks

Paper: From low-level fault modeling to a proven hardening scheme — CC'24 [MDG24]

- Co-designed countermeasure with nice properties!

- Simple implementation on both ends

- HW computes checksum of executed opcodes

- SW tests it before every jump

- Formalized and proven

- Attacks will crash or be detected quickly

- Reasonable performance

- For a strong attacker, 10% time, 2.5x space

- Usual instruction skip CM are 4x time/space

lex-level effects

ther shows that targeted fault attacks can and do defeat

Naturally, using low-level models widens the eletraction

can between the affack and the countermeasure (often an plied during compilation at an IR or back-end level). This

the compiler's late stages. These cross-layer concerns (com-

In order to conquer the complexity of these attacks, se-

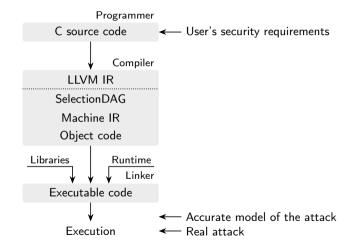

#### Still, we can't be just low-level.

The security property is just "normal behavior or exception".

- ▶ What about denial of service? Real-time violations? Data leaks?

- Also not everything needs to be protected...

#### Requirement:

Source should be able to provide security annotations.

#### Often missing at the SW/HW interface

- ▶ Most hardware countermeasures against faults only do functionality

- Also a social problem!

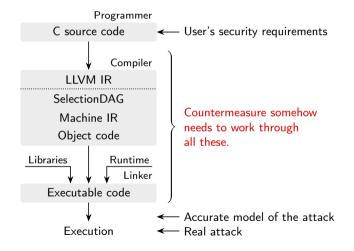

#### ... which only the compiler can properly deal with.

#### Typically:

- ► Harden everything; no control from source code like annotations

- ► Harden close to source: no control of assembly (and pray for -00 to work)

- Compiler optimizations ruin your day

- ► Tricks to avoid breakage: volatile abuse, inline assembly, disable passes...

```

// can you see what's wrong with this?

void *(* volatile memset_ptr)(void *, int, size_t) = &memset;

memset_ptr(array, 0, sizeof array);

```

Glaringly insufficient: subtle bugs, no formal guarantees, always a pain.

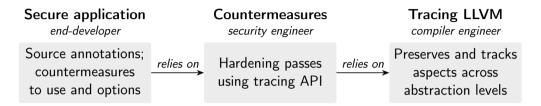

#### Let's make the compiler a first-class objective.

Secure application Countermeasures Tracing LLVM end-developer security engineer compiler engineer Source annotations: Preserves and tracks Hardening passes relies on relies on countermeasures aspects across using tracing API to use and options abstraction levels

#### Let's make the compiler a first-class objective.

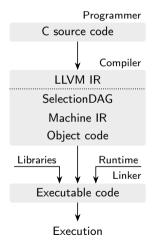

- \* Tracing LLVM: extension of LLVM, currently focused on RISC-V

- ▶ Adds semantic tools that preserve and *trace* elements of the program

- ▶ (Ongoing) Provides an API for querying and accessing traced objects

- ▶ Is intended to be used as a "countermeasure toolbox"

Open-source at https://gricad-gitlab.univ-grenoble-alpes.fr/tracing-llvm

#### Tracing demo #1: types

We want to cleanup all registers containing data related to cardPin when returning.

```

unsigned char ! __attribute__((trace(dataflow))) cardPin[4];

```

#### Tracing demo #1: types

We want to cleanup all registers containing data related to cardPin when returning.

```

unsigned char ! __attribute__((trace(dataflow))) cardPin[4];

```

- ► Traced type constructor "T!"—secretly the identity

- Here we trace the downstream dataflow of cardPin

#### Tracing demo #1: types

We want to cleanup all registers containing data related to cardPin when returning.

```

unsigned char ! __attribute__((trace(dataflow))) cardPin[4];

//

```

- ► Traced type constructor "T!"—secretly the identity

- ► Here we trace the downstream dataflow of cardPin

#### What does this do?

- ► Taint expressions that depend on cardPin in the front-end

- ▶ Prevent the compiler from rewriting the computations

- ▶ Trace them until Machine IR, where we can cleanup all relevant registers

#### Tracing demo #2: wrappers

We want to use hardened booleans (0x55/0xaa) and not have them optimized away.

```

int ! __attribute__((trace(writes))) valid = 0x55:

```

- ► Traces writes to valid, requiring that they occur exactly as written in source

- Compiler can't change the values even if it recognizes a boolean

#### Tracing demo #2: wrappers

We want to use hardened booleans (0x55/0xaa) and not have them optimized away.

```

int ! __attribute__((trace(writes))) valid = 0x55:

```

- ► Traces writes to valid, requiring that they occur exactly as written in source

- ► Compiler can't change the values even if it recognizes a boolean

```

LIVM IR

RISC-V Assembler

simplewrapper void 1 2 closed

; unoptimized

store i32 85, ptr %valid; hidden

li a0, 0x55

```

- ... optimizations can't touch wrappers because it would be incorrect functionally

- ► As a bonus, guaranteed to use the same register for all writes

# Getting strong countermeasures from tracing

I use Tracing LLVM to build a secure verifyPIN function with:

- Basic data-flow integrity (double loads)

- Basic control-flow integrity (Step Counter Incrementation)

- All sensitive data allocated in registers

- Sensitive registers zeroed at exit of function

# Getting strong countermeasures from tracing

I use Tracing LLVM to build a secure verifyPIN function with:

- ► Basic data-flow integrity (double loads)

- Basic control-flow integrity (Step Counter Incrementation)

- ► All sensitive data allocated in registers

- Sensitive registers zeroed at exit of function

- $\rightarrow$  Source

- $\rightarrow$  Source

- $\rightarrow$  Assembly

- $\rightarrow$  Assembly

\* Can have both source annotations and precise assembly code!

# Other features of interest (WIP)

#### Control lowerings:

- ▶ Preserve accesses (like volatile but with register promotion)

- ► Lower C variable to single unique register (all live ranges)

#### Trace source code to target code:

- Erase sensitive registers after function

- Guaranteed correct debug information (up to some optimizations lost)

#### Countermeasure API:

- "What SSA values are myvar right now?"

- "Which two assembly xor do my mask refresh?"

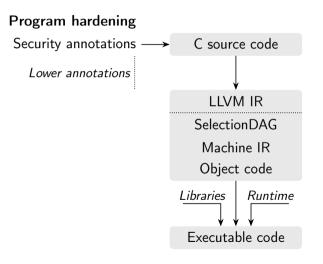

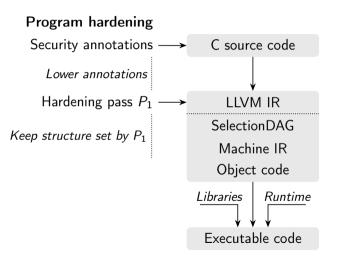

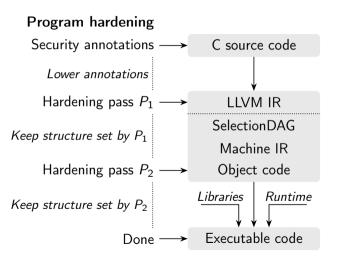

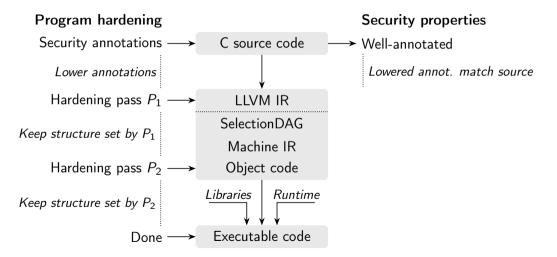

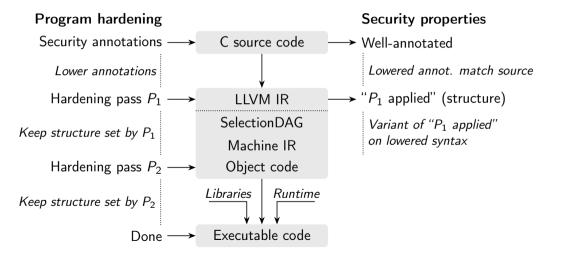

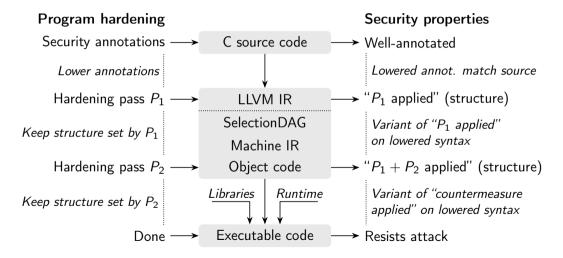

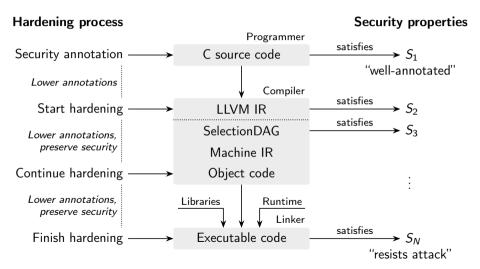

#### Program hardening

# Security properties

#### Security properties

#### Security properties

#### Security properties

# It's like a parallel compilation!

Semantics and secure compilation

# It's like a parallel compilation!

Semantics and secure compilation

# It's like a parallel compilation!

Semantics and secure compilation

# Conclusion

with the compiler, not against

with the compiler, not against

#### My contributions

- 1. Fetch skips countermeasure: software can help with microarch attacks!

- 2. Tracing LLVM: tools and compilation guarantees for writing countermeasures.

- » https://gricad-gitlab.univ-grenoble-alpes.fr/tracing-llvm

with the compiler, not against

#### My contributions

- 1. Fetch skips countermeasure: software can help with microarch attacks!

- 2. Tracing LLVM: tools and compilation guarantees for writing countermeasures.

- » https://gricad-gitlab.univ-grenoble-alpes.fr/tracing-llvm

#### Take-away messages!

- ▶ Use the *compiler* to connect high-level requirements to low-level secure code

- ▶ Position: we should also do that with SW/HW co-design!

with the compiler, not against

#### My contributions

- 1. Fetch skips countermeasure: software can help with microarch attacks!

- 2. Tracing LLVM: tools and compilation guarantees for writing countermeasures.

- » https://gricad-gitlab.univ-grenoble-alpes.fr/tracing-llvm

#### Take-away messages!

- ▶ Use the *compiler* to connect high-level requirements to low-level secure code

- Position: we should also do that with SW/HW co-design!

Questions?

#### Related work

- ➤ Son Tuan Vu's Ph.D [Vu21] (with Karine Heydemann)

much of the same pitch, but only preserves passive observations—within the semantics

- ► The Correctness-Security Gap in Compiler Optimization [DPS15] (2015); What You Get is What You C [SCA18] (2018) earlier dives into the fundamental challenges in secure compilation

- ► CompaSeC [Gei+23] (a combined control- and data-flow protection) showcases how hard it is to compose countermeasures, thus the need to prove

#### References I

- [Als+22]Ihab Alshaer et al. "Variable-Length Instruction Set: Feature or Bug?" In: 2022 25th Euromicro Conference on Digital System Design (DSD). Maspalomas, Spain. IEEE, 2022. ISBN: 978-1-6654-7405-4 DOI: 10 1109/DSD57027 2022 00068

- [DPS15] Vijay D'Silva, Mathias Payer, and Dawn Song, "The Correctness-Security Gap in Compiler Optimization", In: 2015 IEEE Security and Privacy Workshops, 2015, pp. 73–87, DOI: 10.1109/SPW.2015.33.

- [Gei+23] Johannes Geier et al. "CompaSeC: A Compiler-Assisted Security Countermeasure to Address Instruction Skip Fault Attacks on RISC-V". In: Proceedings of the 28th Asia and South Pacific Design Automation Conference, ASPDAC '23, Tokyo, Japan: Association for Computing Machinery, Jan. 2023, pp. 676–682. ISBN: 9781450397834. DOI: 10.1145/3566097.3567925. URL: https://doi.org/10.1145/3566097.3567925.

- [Lau20] Johan Laurent. "Modélisation de fautes utilisant la description RTL de microarchitectures pour l'analyse de vulnérabilité conjointe matérielle-logicielle". Theses. Université Grenoble Alpes, Nov. 2020. URL: https://tel.archives-ouvertes.fr/tel-03167493.

#### References II

- [MDG24] Sébastien Michelland, Christophe Deleuze, and Laure Gonnord. "From low-level fault modeling (of a pipeline attack) to a proven hardening scheme". In: Compiler Construction (CC'24). Edinburgh (Scotland), United Kingdom, Mar. 2024. DOI: 10.1145/3640537.3641570. URL: https://hal.science/hal-04438994.

- [SCA18] Laurent Simon, David Chisnall, and Ross Anderson, "What You Get is What You C: Controlling Side Effects in Mainstream C Compilers". In: 2018 IEEE European Symposium on Security and Privacy (EuroS&P). 2018, pp. 1-15. DOI: 10.1109/EuroSP.2018.00009.

- [Sol+21]Hadi Soleimany et al. "Practical multiple persistent faults analysis". In: Cryptology ePrint Archive (2021).

- [Vu21] Son Tuan Vu. "Optimizing Property-Preserving Compilation". Thèse de doctorat dirigée par Heydemann, Karine et Cohen, Albert Henri Informatique Sorbonne université 2021. PhD thesis. Sorbonne Université, 2021. URL: http://www.theses.fr/2021SORUS435.

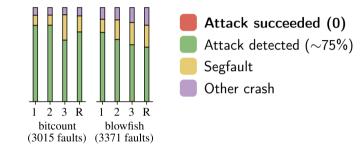

### Fetch skips hardening: validation

#### MiBench benchmarks

- 1. Exhaustive skip

- 2. Exhaustive double-skip

- 3. Exhaustive skip-and-repeat

- R. 2000 random multi-faults

- ▶ 9 programs, 32'000 attacks reached, 0 bypass (0 checksum collision)

- ► Cost: ~10% time, average x2.46 space (similar work: x5 time and space)

These are very good because of the software/hardware combo!

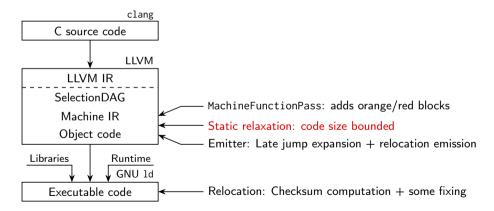

### Fetch skips hardening implementation

► Fetch Skips Hardening is presented as an assembly transform, but...

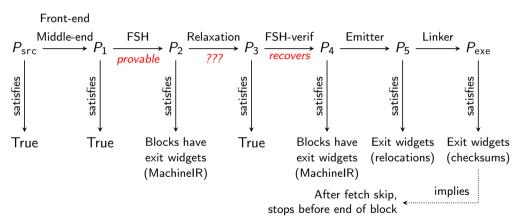

# Model of multi-pass hardening

# Security properties of fetch skips hardening

Almost never talks about fetch skips.

# ... leading to some of the most robust guarantees

- ► To reason about the attack, extend the semantics of assembler!

- Describe how fetches work to clear the abstraction gap

- ► Fetch rules (right): describe fetches + attacks

- ► Step rules (not shown): decoding/execution

## Proven security guarantee

If you fetch skip, the program will stop/crash before the end of the current block.

Multi-fault attacks too (unless checksum collision—usually impossible).

$$\frac{\mathsf{NOFAULT}}{(\mathsf{PC}, \rho) \ a \Rightarrow [a] \ (\mathsf{PC}, [a])}$$

$$\frac{\mathsf{S32}(k)}{(\mathsf{PC},\rho)\ a\Rightarrow [a+4k]\ (\mathsf{PC}+4k,[a+4k])}$$

$$\frac{\text{S&R32}}{(\text{PC}, \rho) \ a \Rightarrow \rho \ (\text{PC}, [a])}$$